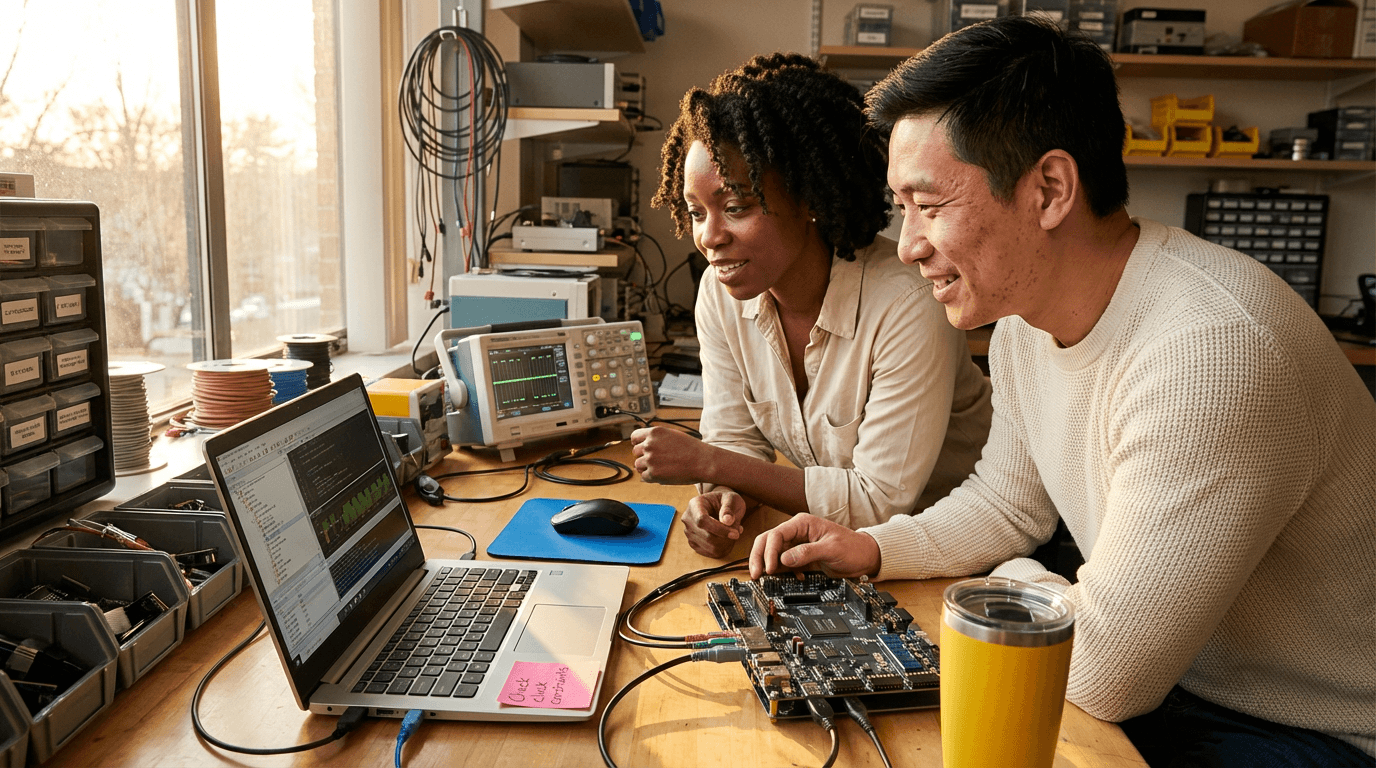

คอร์ส VHDL

เชี่ยวชาญ VHDL สำหรับอิเล็กทรอนิกส์ในโลกจริง: ออกแบบลอจิก FPGA แบบซิงโครนัส สร้างตัวกรองค่าเฉลี่ยเคลื่อนที่ หน่วยควบคุมเซ็นเซอร์ที่แข็งแกร่ง เขียน testbench ที่มีประสิทธิภาพและสถานการณ์ยืนยันผลที่ตรงตามข้อจำกัดด้านจังหวะ ความน่าเชื่อถือ และการนำไปใช้งาน

ภาระงานที่ยืดหยุ่นตั้งแต่ 4 ถึง 360 ชั่วโมง

ใบรับรองที่ถูกต้องในประเทศของคุณ

ฉันจะเรียนรู้อะไร?

คอร์ส VHDL นี้ช่วยสร้างทักษะการออกแบบ ยืนยันผล และนำไปใช้งาน RTL สอดคล้องแบบซิงโครนัสที่เชื่อถือได้บน FPGA อย่างรวดเร็ว คุณจะเรียนพื้นฐาน VHDL กระบวนการแบบมีนาฬิกา ประเภทข้อมูล และสไตล์การเขียนโค้ดที่สะอาด จากนั้นนำไปสร้างตัวกรองค่าเฉลี่ยเคลื่อนที่ หน่วยควบคุมเซ็นเซอร์ และ testbench ที่แข็งแกร่ง คอร์สจบด้วยกลยุทธ์การจำลองและข้อจำกัด FPGA ในทางปฏิบัติ เพื่อสร้างการออกแบบดิจิทัลที่มีประสิทธิภาพและคาดเดาได้

ข้อดีของ Elevify

พัฒนาทักษะ

- ออกแบบ VHDL RTL: สร้างลอจิก FPGA แบบซิงโครนัสสะอาดสำหรับระบบเซ็นเซอร์จริง

- DSP ค่าเฉลี่ยเคลื่อนที่: นำไปใช้งานตัวกรอง FIR 8 บิตด้วยคณิตศาสตร์จุดทศนิยมคงที่ปลอดภัย

- Testbench VHDL: เขียนการทดสอบที่อ่านง่ายและแน่นอนด้วย assertions และการตรวจสอบ

- การปรับให้เหมาะสม FPGA: ชั่งน้ำหนักจังหวะ พื้นที่ และพลังงานสำหรับบล็อก DSP และควบคุมขนาดเล็ก

- ทักษะการยืนยันผล: ใช้การจำลอง คลื่นรูป และกรณีขอบเขตเพื่อพิสูจน์พฤติกรรม

สรุปที่แนะนำ

ก่อนเริ่มต้น คุณสามารถเปลี่ยนบทและภาระงาน เลือกบทที่ต้องการเริ่มต้น เพิ่มหรือลบบท เพิ่มหรือลดภาระงานของหลักสูตร.ความคิดเห็นจากผู้เรียนของเรา

As suas aulas são perfeitas. Adquiri o pacote de um ano e, finalmente, tenho a oportunidade de acompanhar diversos temas do meu interesse sem precisar mudar de plataforma... agradeço por tudo o que fazem, já recomendei vocês a outras pessoas...

Giulio CarloAluno de Marketing Digital

Eu gosto de como as lições são direto ao ponto e como eu consigo alterar capítulos e pular conteúdos que não preciso.

Mariana FerresAluna de Fotografia

Gosto do conteúdo e do modo de apresentação e transcrição de vídeos, o que acelera o processo!

Luciana AlvarengaAluna de Design de Unhas

A plataforma é rápida, simples de usar. A diversidade de conteúdo e os vídeos complementares ajudam muito no aprendizado.

Giulio CarloAluno de Engenharia de Prompt

คำถามที่พบบ่อย

Elevify คืออะไร? มันทำงานอย่างไร?

หลักสูตรมีใบรับรองหรือไม่?

หลักสูตรฟรีหรือไม่?

ชั่วโมงการทำงานของหลักสูตรคืออะไร?

หลักสูตรเป็นอย่างไร?

หลักสูตรทำงานอย่างไร?

ระยะเวลาของหลักสูตรคืออะไร?

ค่าใช้จ่ายหรือราคาของหลักสูตรคืออะไร?

EAD หรือหลักสูตรออนไลน์คืออะไรและทำงานอย่างไร?

หลักสูตร PDF