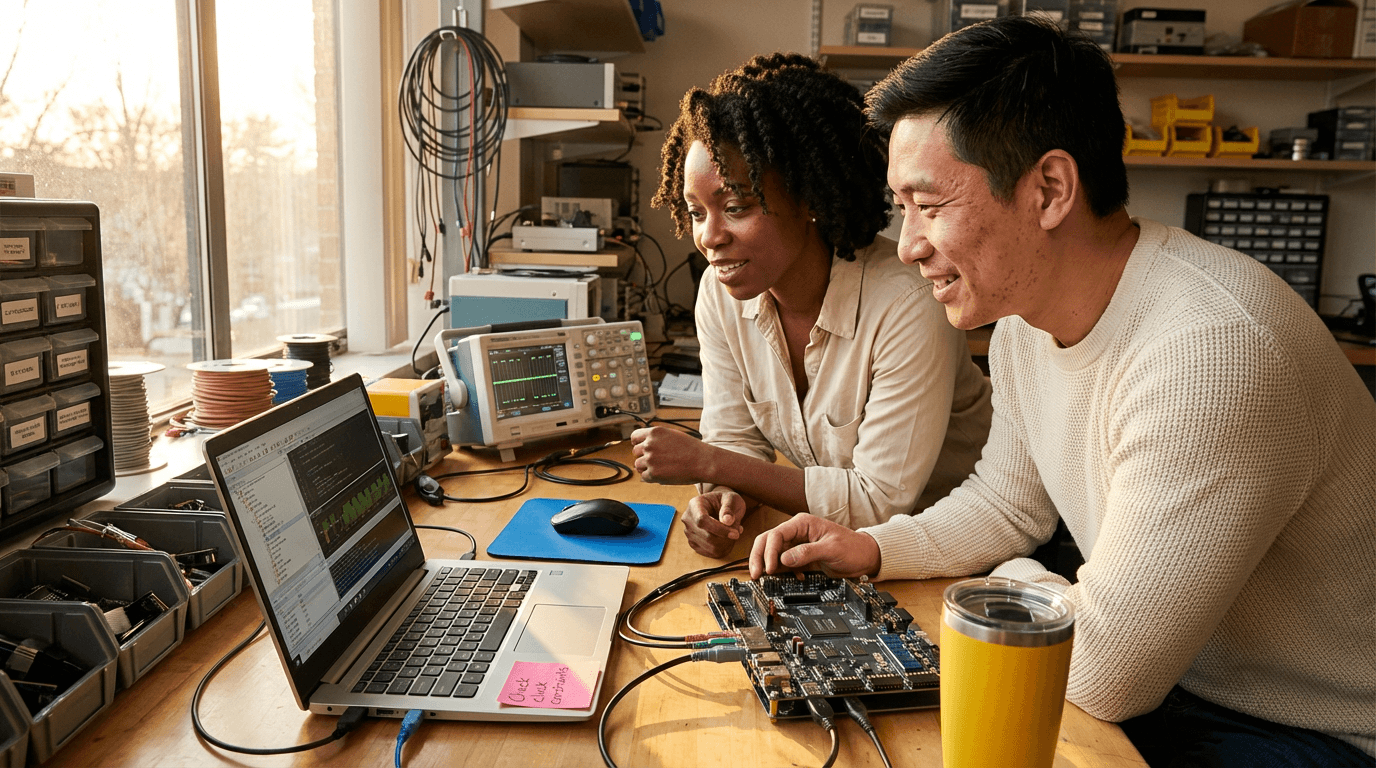

קורס VHDL

שליטה ב-VHDL ליישומים אלקטרוניים אמיתיים: תכנון לוגיקה סינכרונית ל-FPGA, בניית מסנני ממוצע נע, יצירת יחידות בקרת חיישנים חזקות, וכתיבת סביבות בדיקה ואימות יעילות העומדות בדרישות תזמון, אמינות ויישום.

עומס לימוד גמיש בין 4 ל-360 שעות

תעודה תקפה במדינתכם

מה אלמד?

קורס VHDL זה בונה במהירות את הכישורים הדרושים לתכנון, אימות ויישום RTL סינכרוני אמין על FPGA. תלמדו יסודות VHDL, תהליכים מבוססי שעון, סוגי נתונים וסגנון קידוד נקי, תיישמו מסנן ממוצע נע, יחידת בקרת חיישן וסביבות בדיקה חזקות. הקורס מסתיים באסטרטגיות סימולציה ומגבלות FPGA מעשיות ליצירת עיצובים דיגיטליים יעילים וצפויים.

היתרונות של Elevify

פיתוח מיומנויות

- תכנון RTL ב-VHDL: בניית לוגיקה סינכרונית נקייה ל-FPGA עבור מערכות חיישנים אמיתיות.

- ממוצע נע DSP: יישום מסנני FIR ב-8 ביט עם חישובי נקודה קבועה בטוחים.

- סביבות בדיקה ב-VHDL: כתיבת בדיקות קריאות ונחושת עם אישורים ובדיקות.

- אופטימיזציה ל-FPGA: שקלול תזמון, שטח וצריכת חשמל עבור בלוקי DSP ובקרה קטנים.

- מיומנויות אימות: שימוש בסימולציה, גלי תדר ותרחישי קצה להוכחת התנהגות.

סיכום מוצע

לפני שמתחילים, ניתן לשנות את הפרקים ואת עומס הלימוד. בחרו באיזה פרק להתחיל. הוסיפו או הסירו פרקים. הגדילו או הקטינו את עומס הקורס.מה הסטודנטים שלנו אומרים

שאלות נפוצות

מי זו Elevify? איך זה עובד?

האם יש תעודות לקורסים?

האם הקורסים חינמיים?

מהו היקף השעות של הקורס?

איך נראים הקורסים?

איך הקורסים עובדים?

מה משך הקורסים?

מה העלות או המחיר של הקורסים?

מהו קורס מקוון (EAD) ואיך הוא עובד?

קורס PDF