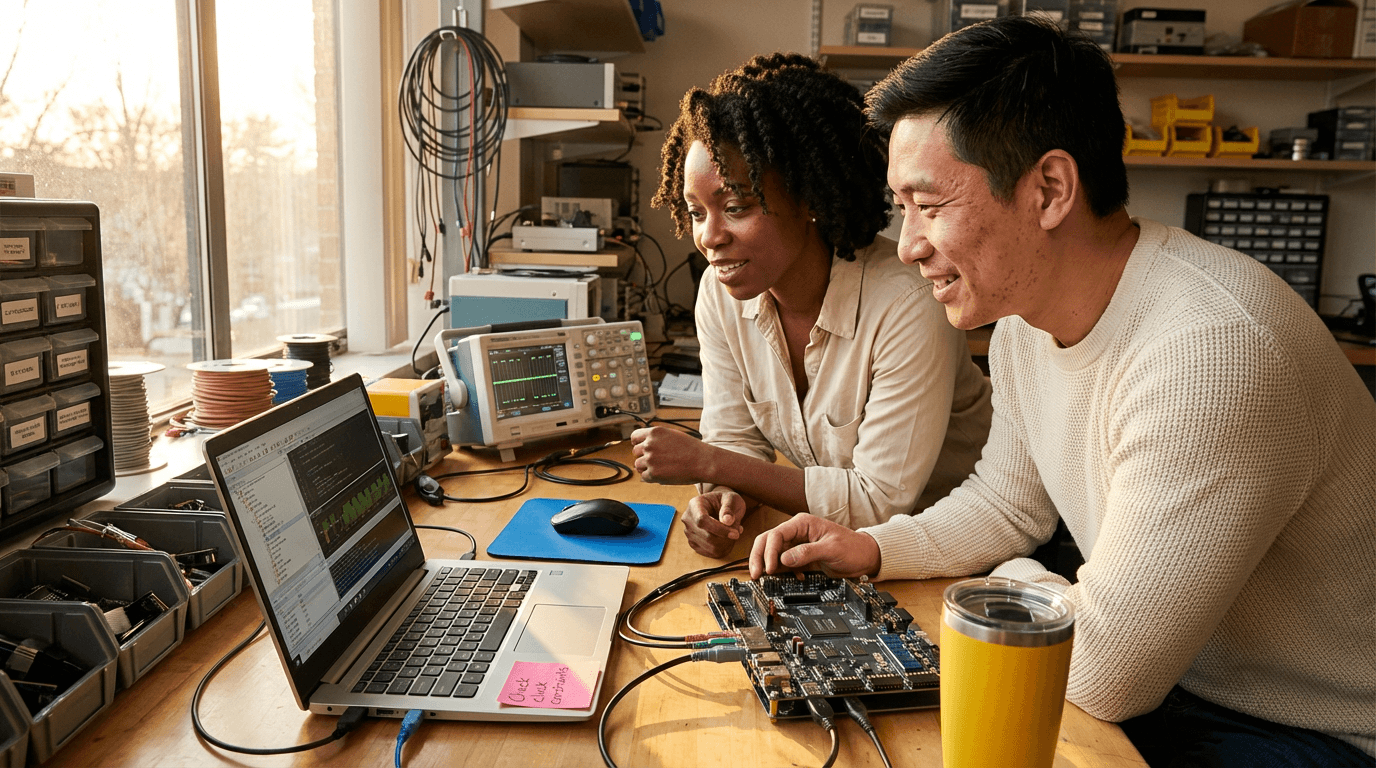

دورة VHDL

إتقان VHDL للإلكترونيات الواقعية: تصميم منطق FPGA متزامن، بناء مرشحات المتوسط المتحرك، إنشاء وحدات تحكم مستشعرات قوية، وكتابة اختبارات فعالة وسيناريوهات تحقق تلبي قيود التوقيت والموثوقية والتنفيذ.

من 4 إلى 360 ساعة عبء دراسي مرن

شهادة معتمدة في بلدك

ماذا سأتعلم؟

تبني هذه الدورة بسرعة المهارات اللازمة لتصميم وتفعيل وتنفيذ منطق RTL متزامن موثوق على FPGA. ستتعلم أساسيات VHDL وعمليات الساعة وأنواع البيانات وأسلوب البرمجة النظيف، ثم تنفذ مرشح متوسط متحرك ووحدة تحكم مستشعر واختبارات قوية. تنتهي الدورة باستراتيجيات المحاكاة وقيود FPGA العملية لإنشاء تصاميم رقمية فعالة ومتوقعة.

مزايا Elevify

طور مهاراتك

- تصميم VHDL RTL: بناء منطق FPGA متزامن نظيف لأنظمة المستشعرات الحقيقية.

- معالجة المتوسط المتحرك DSP: تنفيذ مرشحات FIR بـ8 بت مع حسابات نقطة ثابتة آمنة.

- اختبارات VHDL: كتابة اختبارات قابلة للقراءة ومحددة باستخدام الادعاءات والتحققات.

- تحسين FPGA: وزن التوقيت والمساحة والطاقة لكتل DSP والتحكم الصغيرة.

- مهارات التحقق: استخدام المحاكاة والموجات والحالات الحدية لإثبات السلوك.

الملخص المقترح

قبل البدء، يمكنك تغيير الفصول والعبء الدراسي. اختر الفصل الذي تريد البدء به. أضف أو احذف الفصول. زد أو قلل عبء الدورة.ماذا يقول طلابنا

دروسكم مثالية. اشتريت باقة السنة الواحدة وأخيرًا أصبحت لدي الفرصة لمتابعة مواضيع متنوعة تهمني دون الحاجة لتغيير المنصة... أشكركم على كل ما تقدمونه، وقد أوصيت بكم بالفعل لأشخاص آخرين...

Giulio Carloطالب التسويق الرقمي

أعجبني كيف أن الدروس مباشرة إلى النقطة وكيف يمكنني التنقل بين الفصول وتخطي المحتوى الذي لا أحتاجه.

Mariana Ferresطالبة التصوير الفوتوغرافي

أحببت المحتوى وأسلوب العرض ونسخ الفيديو، مما يسرّع العملية!

Luciana Alvarengaطالبة تصميم الأظافر

المنصة سريعة وسهلة الاستخدام. تنوع المحتوى والفيديوهات التكميلية يساعدان حقًا في التعلم.

André Felipeطالب هندسة البرومبت

الأسئلة الشائعة

من هي Elevify؟ كيف تعمل؟

هل الدورات تحتوي على شهادات؟

هل الدورات مجانية؟

ما هو عبء الدورة؟

كيف هي الدورات؟

كيف تعمل الدورات؟

ما هي مدة الدورات؟

ما هو سعر أو تكلفة الدورات؟

ما هو التعليم عن بعد أو الدورة عبر الإنترنت وكيف تعمل؟

دورة PDF